WORKING X3T10

DRAFT 791D

Revision 4c

Information technology - AT Attachment Interface for Disk Drives

This is a draft proposed American National Standard of Accredited Standards Committee X3. As such this is not a completed standard. The X3T10 Technical Committee may modify this document as a result of comments received during public review and its approval as a standard.

Copyright 1994, Computer and Business Equipment Manufacturers Association. Permission is granted to members of X3, its technical committees, and their associated task groups to reproduce this document for the purposes of X3 standardization activities without further permission, provided this notice is included. All other rights are reserved.

ASC X3T10 Technical Editor: Lawrence J. Lamers

Adaptec

691 South Milpitas Blvd Milpitas, CA 95035

USA

Telephone: 408-957-7817

Facsimile: 408-957-7193

Email: ljlamers@aol.com

Reference number ANSI X3.221 - 199x

#### POINTS OF CONTACT:

X3T10 Chair

John B. Lohmeyer

X3T10 Vice-Chair

Lawrence J. Lamers

NCR Corporation Adaptec

1635 Aeroplaza Drive 691 South Milpitas Blvd Colo Spgs, CO 80916 Milpitas, CA 95035

Tel: (719) 573-3362 Tel: 408-957-7817

Fax: (719) 597-8225 Fax: 408-957-7193

Email: john.lohmeyer@ftcollinsco.ncr.com Email: ljlamers@aol.com

X3 Secretariat

Lynn Barra

Administrator Standards Processing

X3 Secretariat Telephone: 202-626-5738

1250 Eye Street, NW Suite 200 Facsimile: 202-638-4922

Washington, DC 20005 Email: lbarra@cbema.org

SFF

SFF Faxback 408-741-1600

ATA Rflector

Internet address for subscription to the reflector:  $\verb|majordomo@dt.wdc.com|$

Internet address for distribution via reflector: ata@dt.wdc.com

X3T10 Bulletin Board 719-574-0424

Document Distribution

Global Engineering Telephone: 303-792-2181 or 15 Inverness Way East 800-854-7179

Englewood, CO 80112-5704 Facsimile: 303-792-2192

### ABSTRACT

This standard defines the AT Attachment Interface. This standard defines an integrated bus interface between disk drives and host processors. It provides a common point of attachment for systems manufacturers, system integrators, and suppliers of intelligent peripherals.

## DOCUMENT STATUS

| Revision 4c<br>Revision 4b | -<br>- | incorporates ANSI editorial changes. revised ANSI patent statement per X3. |

|----------------------------|--------|----------------------------------------------------------------------------|

| Revision 4                 | -      | developed as a result of comments received on X3T9.2                       |

|                            |        | letter ballot.                                                             |

| Revision 3.3               | -      | developed as a result of the comments received                             |

|                            |        | during public review.                                                      |

| Revision 3.1               | -      | forwarded in August 1991 from X3T9.2 to X3T9 for                           |

|                            |        | further processing as an American National Standard.                       |

## Contents

| Foreword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>         |     |      |                                       | age<br>/ii                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|------|---------------------------------------|-----------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>         |     |      |                                       | хi                                                                                            |

| 1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <br>         |     |      |                                       | 1                                                                                             |

| 2 Normative references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>         |     |      |                                       | 1                                                                                             |

| 3 Definitions, symbols, and abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <br>         |     |      |                                       | 1<br>1<br>2                                                                                   |

| 4 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <br>         |     |      |                                       | 2<br>2<br>2                                                                                   |

| 5 Interface cabling requirements 5.1 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br><br><br> |     | <br> |                                       | 3<br>4<br>4<br>5<br>5<br>6                                                                    |

| 6 Physical interface. 6.1 Signal conventions. 6.2 Signal summary. 6.3 Signal descriptions 6.3.1 CS1FX- (drive chip select 0). 6.3.2 CS3FX- (drive chip select 1). 6.3.3 DAO-2 (Drive address bus). 6.3.4 DASP- (Drive active/drive 1 present). 6.3.5 DDO-DD15 (Drive data bus). 6.3.6 DIOR- (Drive I/O read). 6.3.7 DIOW- (Drive I/O write). 6.3.8 DMACK- (DMA acknowledge) (Optional). 6.3.9 DMARQ (DMA request) (Optional). 6.3.10 INTRQ (Drive interrupt). 6.3.11 IOCS16- (Drive 16-bit I/O). 6.3.12 IORDY (I/O channel ready) (Optional). 6.3.13 PDIAG- (Passed diagnostics). 6.3.14 RESET- (Drive reset). 6.3.15 SPSYNC:CSEL (Spindle synchronization/cable select). 6.3.16 SPSYNC (Spindle synchronization) (Optional). 6.3.17 CSEL (Cable select) (Optional). |              | Opt | <br> | · · · · · · · · · · · · · · · · · · · | 6<br>6<br>7<br>8<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>10<br>10<br>10<br>11<br>11<br>11<br>11 |

| 7 Logical interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |     |      |                                       | 12<br>12                                                                                      |

|   | 7.1.1 Bit conventions                                          |   |   | 12 |

|---|----------------------------------------------------------------|---|---|----|

|   | 7.1.2 Environment                                              |   |   | 12 |

|   | 7.2 I/O register descriptions                                  |   |   | 13 |

|   | 7.2.1 Alternate status register                                |   |   | 14 |

|   | 7.2.2 Command register                                         |   |   | 14 |

|   | 7.2.3 Cylinder high register                                   |   |   | 14 |

|   | 7.2.4 Cylinder low register                                    | • | • | 14 |

|   | 7.2.5 Data register                                            |   |   | 14 |

|   | 7.2.5 Data register                                            | • | • | 14 |

|   | 7.2.6 Device control register                                  | • | • |    |

|   | 7.2.7 Drive address register                                   | ٠ | • | 15 |

|   | 7.2.8 Drive/head register                                      | ٠ | • | 15 |

|   |                                                                |   |   | 15 |

|   | 7.2.10 Features register                                       |   |   | 16 |

|   | 7.2.11 Sector count register                                   |   |   | 16 |

|   | 7.2.12 Sector number register                                  |   |   | 16 |

|   | 7.2.13 Status register                                         |   |   | 17 |

|   |                                                                |   |   |    |

| 8 | Programming requirements                                       |   |   | 18 |

| 0 | 8.1 Reset response                                             |   |   | 18 |

|   | 0.1 Reset lesponse                                             | • | • | 19 |

|   | 8.2 Translate mode                                             | • | • |    |

|   | 8.3 Power conditions                                           | ٠ | • | 19 |

|   | 8.4 Error posting                                              | • | • | 20 |

| _ |                                                                |   |   |    |

| 9 |                                                                | • | • | 21 |

|   | 9.1 Acknowledge media change (removable)                       |   |   | 23 |

|   | 9.2 Boot - post-boot (removable)                               |   |   | 23 |

|   | 9.2 Boot - post-boot (removable)                               |   |   | 23 |

|   | 9.4 Check power mode                                           |   |   | 23 |

|   | 9.5 Door lock (removable)                                      |   |   | 23 |

|   | 9.6 Door unlock (removable)                                    |   |   | 23 |

|   | 9.7 Execute drive diagnostic                                   | • | • | 23 |

|   | 9.8 Format track                                               | • | • | 24 |

|   | 9.0 FUIIIIAL LIACK                                             | • | • | 25 |

|   | 9.9 Identify drive                                             | ٠ | • |    |

|   | 9.9.1 Word 1: Number of cylinders                              | • | • | 27 |

|   | 9.9.2 Word 3: Number of heads                                  | • | • | 27 |

|   | 9.9.3 Word 4: Number of unformatted bytes per track            |   |   | 27 |

|   | 9.9.4 Word 5: Number of unformatted bytes per sector           |   |   | 27 |

|   | 9.9.5 Word 6: Number of sectors per track                      |   |   | 27 |

|   | 9.9.6 Word 10-19: Serial Number                                |   |   | 27 |

|   | 9.9.7 Word 20: Buffer Type                                     |   |   | 27 |

|   | 9.9.8 Word 22: ECC bytes available on read/write long commands |   |   | 27 |

|   | 9.9.9 Word 23-26: Firmware revision                            |   |   | 27 |

|   | 9.9.10 Word 27-46: Model number                                | • | • | 28 |

|   | 9.9.11 Word 51: PIO data transfer cycle timing mode            |   |   | 28 |

|   |                                                                |   |   |    |

|   | 9.9.12 Word 52: DMA data transfer cycle timing mode            |   |   | 28 |

|   | 9.9.13 Word 54: Number of current cylinders                    |   |   | 28 |

|   | 9.9.14 Word 55: Number of current heads                        |   |   | 28 |

|   | 9.9.15 Word 56: Number of current sectors per track            |   |   | 28 |

|   | 9.9.16 Word 57-58: Current capacity in sectors                 |   |   | 28 |

|   | 9.9.17 Word 59: Multiple sector setting                        |   |   | 28 |

|   | 9.9.18 Word 60-61: Total number of user addressable sectors    |   |   | 28 |

|   | 9.9.19 Word 62: Single word DMA transfer                       |   |   | 28 |

|   | 9.9.20 Word 63: Multiword DMA transfer                         |   |   | 29 |

|   | 9.10 Idle                                                      |   |   |    |

|   |                                                                | • | • |    |

|    | 9.11 Idle immediate               |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 29 |

|----|-----------------------------------|----|-----|-----|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|----|

|    | 9.12 Initialize drive parameters. |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 29 |

|    | 9.13 NOP                          |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 29 |

|    | 9.14 Read buffer                  |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 30 |

|    | 9.15 Read DMA                     |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 30 |

|    | 9.16 Read long                    |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 30 |

|    | 9.17 Read multiple command        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 30 |

|    | 9.18 Read sector(s)               |    | •   | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | 31 |

|    | 9.19 Read verify sector(s)        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 31 |

|    | 9.20 Recalibrate                  |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 32 |

|    | 9.21 Seek                         |    | •   |     | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | 32 |

|    | 9.22 Set features                 |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 32 |

|    | 9.23 Set multiple mode            |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 33 |

|    | 9.24 Sleep                        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 33 |

|    | 9.24 Sieep                        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 34 |

|    | 4                                 |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |

|    | 9.26 Standby immediate            |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 34 |

|    | 9.27 Write buffer                 |    | •   |     | •   | ٠  | ٠ | • | • | • | • | • | • | • | • | • | • | • | 34 |

|    | 9.28 Write DMA                    |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 34 |

|    | 9.29 Write long                   |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 35 |

|    | 9.30 Write multiple command       |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 35 |

|    | 9.31 Write same                   |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 36 |

|    | 9.32 Write sector(s)              |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 36 |

|    | 9.33 Write verify                 |    |     |     | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | 37 |

|    | _                                 |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |

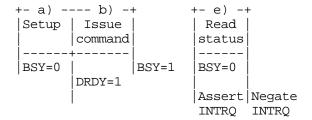

| 10 | Protocol overview                 |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 37 |

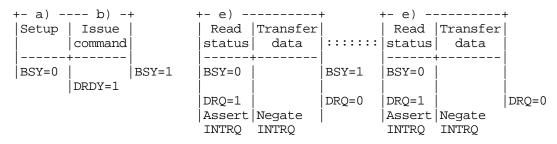

|    | 10.1 PIO data in commands         |    | •   |     | •   | ٠  | • | • | • | • | • | • | • | • | • | • | • | • | 37 |

|    | 10.1.1 PIO read command           |    |     |     | •   | •  | • | • | • | • | • | • | • | • | • |   | • | • | 37 |

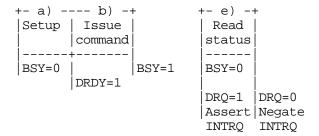

|    | 10.1.2 PIO Read aborted command . |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

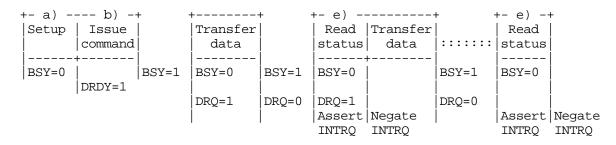

|    | 10.2 PIO data out commands        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

|    | 10.2.1 PIO write command          |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

|    | 10.2.2 PIO write aborted command. |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

|    | 10.3 Non-data commands            |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 39 |

|    | 10.4 Miscellaneous commands       |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 39 |

|    | 10.5 DMA data transfer commands ( | or | pt: | ion | nal | ). |   |   |   |   |   |   |   |   |   |   |   |   | 39 |

|    | 10.5.1 Normal DMA transfer        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 40 |

|    | 10.5.2 Aborted DMA transfer       |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 40 |

|    | 10.5.3 Aborted DMA Command        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 40 |

|    |                                   |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |

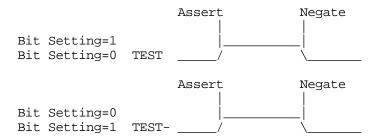

| 11 | Timing                            |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

|    | 11.1 Deskewing                    |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

|    | 11.2 Symbols                      |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

|    | 11.3 Terms                        |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

|    | 11.4 Data Transfers               |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 42 |

|    | 11.5 Power on and hard reset      |    |     |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   | 45 |

# Figures

|                 | interface to emb |              |         |   |       |   |       |   |   |    |

|-----------------|------------------|--------------|---------|---|-------|---|-------|---|---|----|

|                 | interface to cor |              |         |   |       |   |       |   |   |    |

|                 | in connector mou |              |         |   |       |   |       |   |   |    |

|                 | e select         |              |         |   |       |   |       |   |   |    |

|                 | data transfer to |              |         |   |       |   |       |   |   |    |

|                 | Y timing require |              |         |   |       |   |       |   |   |    |

|                 | le word DMA data |              |         |   |       |   |       |   |   | 43 |

|                 | iword DMA data t |              |         |   |       |   |       |   |   |    |

| Figure 10 - Res | set sequence     |              |         | • |       | • | <br>• | • | • | 45 |

| Annexes         |                  |              |         |   |       |   |       |   |   |    |

| Annex A Di      | agnostic and res | set consider | ations  | • | <br>٠ |   |       | • | • | 46 |

| Annex B Di      | agnostic and res | set consider | ations. | • |       |   |       |   |   | 50 |

| Annex C Sm      | all form factor  | connectors   |         |   |       |   |       |   |   | 55 |

#### Foreword

(This foreword is not part of American National Standard X3.221-199x.)

This standard defines the AT Attachment Interface. This standard defines an integrated bus interface between disk drives and host processors. It provides a common point of attachment for systems manufacturers, system integrators, and suppliers of intelligent peripherals.

This standard was developed by Task Group X3T9.2 of Accredited Standards Committee X3 during 1986-90. The standards approval process started in 1991. This document includes annexes which are informative and are not considered par of the standard.

Requests for interpretation, suggestions for improvement and addenda, or defect reports are welcome. They should be sent to the X3 Secretariat, Computer and Business Equipment Manufacturers Association, 1250 Eye Street, NW, Suite 200, Washington, DC 20005-3922.

This standard was processed and approved for submittal to ANSI by Accredited Standards Committee on Information Processing Systems, X3. Committee approval of the standard does not necessarily imply that all committee members voted for approval. At the time it approved this standard, the X3 Committee had the following members:

James D. Converse, Chair Donald C. Loughry, Vice-Chair Joanne M. Flanagan, Secretary

| AMP, Inc                                                 |

|----------------------------------------------------------|

|                                                          |

| Apple Computer                                           |

| Certification of Professionals (AICCP) Kenneth Zemrowski |

| AT&T/NCR                                                 |

| Thomas F. Frost (Alt.)                                   |

| Boeing Company                                           |

| Andrea Vanosdoll (Alt.)                                  |

| Bull HN Information Systems, Inc                         |

| Compaq Computer Corporation                              |

| Digital Equipment Corporation Delbert Shoemaker          |

| Kevin Lewis (Alt.)                                       |

| Eastman Kodak                                            |

| Michael Nier (Alt.)                                      |

| GUIDE International                                      |

| Harold Kuneke (Alt.)                                     |

| Organization Represented  Hewlett-Packard                                 |

|---------------------------------------------------------------------------|

| Hughes Aircraft Company                                                   |

| National Communication Systems                                            |

| Northern Telecom, Inc                                                     |

| Neville & Associates                                                      |

| SHARE, Inc                                                                |

| Sony Corporation                                                          |

| Sun Microsystems                                                          |

| 3M Company                                                                |

| Unisys Corporation                                                        |

| U.S. Department of Defense                                                |

| U.S. Department of Energy                                                 |

| U.S. General Services Administration Douglas Arai Larry L. Jackson (Alt.) |

| Wintergreen Information Services Joun Wheeler Xerox Corporation           |

| G 1                                                                       |

Subcommittee X3T9 on I/O Interface, which reviewed this standard, had the following members:

| Del Shoemaker, Chair | Charles Brill |

|----------------------|---------------|

| Bob Fink, Vice-Chair | Bill Burr     |

Bill Burr

Jeff Connell

Steve Cooper

Roger Cummings

Rhonda Dirvin

Jim Hamstra

Dave Husak

Reinhard Knerr

Larry Lamers

George Michael

Gene Milligan

Doug Morrissey

Steven Myers

Roger Pandanda

Everett Rigsbee, III

Floyd Ross

Amit Shah

Jeff Stone

Pat Thaler

Don Tolmie

Schelto van Doorn

Jim Vogt

Carl Zeitler

Working Group X3T9.2 on Lower Level Interface, which developed this standard, had the following members:

John B. Lohmeyer, Chair I. Dal Allan, Vice-Chair Lawrence J. Lamers, Secretary Mr. Alan R. Olson Mr. D. Michael Mr. Paul Wolf Mr. Norm Harris Robinson (Alt.) Mr. Stephen G. Mr. Joe Lawlor Mr. Anthony Fung Mr. Charles Brill Finch (Alt.) Mr. Jeff Rosa Mr. Mike Yokoyama Mr. John F. Osborn Mr. Jan V. Dedek Mr. Erich Oetting (Alt.) Mr. Scott Smyers Mr. Robert N. Mr. Heinz Mr. Tom Debiec Snively Piorunneck (Alt.) Mr. Edward Hrvatin Mr. John Moy Mr. Steve Chang Mr. Clifford E. Mr. Ricardo (Alt.) Strang Jr. Dominguez Mr. Raymond Gilson Ms. Janet Schank Mr. Harvey (Alt.) Mr. Kurt Witte Waltersdorf Mr. Lam Dang Mr. Joe Chen Mr. James Mang (Alt.) Mr. Edward Haske Mr. Chuck Duquette Mr. John Geldman Mr. Stephen R. Mr. Peter (Alt.) Mr. Nicos Syrimis Cornaby Dougherty Mr. Gary S. Mr. Jeff Stai (Alt.) Mr. Doug Piper Mr. Dave Weber Peterson Mr. Charles Monia Mr. Greg Leonhardt (Alt.) Mr. Skip Jones Mr. George Su Mr. Edward Lappin Mr. Rick Heidick (Alt.) Mr. Robert Liu (Alt.) Mr. Paul Thompson Mr. Steve Caron Mr. Wayne Roen (Alt.) Mr. Erwin Hauck (Alt.) Mr. Greg McSorley Mr. Jeffrey L. Mr. Al Wilhelm (Alt.) Williams (Alt.) Mr. William Dallas Mr. Peter Stevens Mr. Neil T. (Alt.) Dr. Sam Wanamaker (Alt.) Mr. Edward A. Karunanithi Mr. Bob Whiteman Gardner (Alt.) Mr. David McFadden (Alt.) Mr. Douglas Hagerman (Alt.) Mr. George Penokie Mr. Michael Mr. David Lawson Wingard (Alt.) Dr. William Ham Mr. Geoff Barton Mr. Gary Porter (Alt.) Mr. David H. Shaff (Alt.) Mr. John Morse Mr. Robert Bellino Mr. Jon Abilay (Alt.) Ms. Donna Pope (Alt.) Mr. Ralph Weber Mr. Bob Masterson Mr. Harlan Andrews (Alt.) Mr. Joe Dambach Mr. Paul R. Nitza (Alt.) Mr. Robbie Mr. James Blair (Alt.) Shergill (Alt.) Mr. D. W. Spence Mr. Mike Eneboe Mr. Bruce Anderson (Alt.) Mr. Stephen F. (Alt.) Mr. Tony Kempka Mr. Ray Kubick Heil (Alt.) Mr. James McGrath (Alt.) Mr. Jim Luttrull Mr. Dennis Pak Dr. Tetsuro (Alt.) Mr. Fred Yamamoto Motoyoma (Alt.) (Alt.)

Ms. Chris Borgers (Alt.) Ms. Lingling Polican (Alt.) Mr. Kurt Chan (Alt.) Mr. Russell Smith (Alt.) Mr. Danny Yeung (Alt.) Mr. Hiroshi Minawa (Alt.) Mr. Paul Anderson (Alt.) Mr. Gerald Marazas (Alt.) Mr. Gary R. Stephens (Alt.) Mr. David Buyze (Alt.) Mr. Robert D. Allgood (Alt.) Mr. Gary Brandvold (Alt.) Mr. David J. Fox (Alt.) Mr. Chuck Grant (Alt.) Mr. David Thayer (Alt.) Mr. Ron Roberts (Alt.) Mr. John Cannon (Alt.) Mr. Jim McGrath (Alt.) Mr. John Goldie (Alt.) Mr. Manish Gupta (Alt.) Ms. Lessie Ortega de Widman (Alt.) Mr. Ernest Luttig (Alt.) Mr. Charles I. Yang (Alt.) Mr. Richard Blackborow (Alt.) Mr. Satwinder S. Mangat (Alt.) Mr. Gerald Houlder (Alt.) Mr. Hale Landis (Alt.)

Mr. Gene Milligan (Alt.) Mr. Daniel E. Moczarny (Alt.) Mr. Greg Walker (Alt.) Mr. Roger Cummings (Alt.) Mr. Vit Novak (Alt.) Mr. Pete Tobias (Alt.) Mr. Alan Wetzel (Alt.) Mr. Ron Scot (Alt.) Mr. Dennis Mellinger (Alt.) Mr. Arlan P. Stone (Alt.) Mr. Tak Asami (Alt.) Mr. Shishir Shah (Alt.) Mr. E.J. Mondor (Alt.) Mr. Geoff Gorbold (Alt.)

#### Introduction

ANSI X3.221-199x does not replace any existing standard.

The clauses contain material as described below.

| Clause 1             | describes the scope;                                        |

|----------------------|-------------------------------------------------------------|

| Clause 2             | lists the normative references;                             |

| Clause 3             | provides a glossary common to the whole document;           |

| Clause 4             | provides descriptions and conventions;                      |

| Clause 5             | describes the electrical and mechanical characteristics;    |

| Clause 6             | describes the signals of the AT Attachment Interface;       |

| Clause 7             | describes the registers of the AT Attachment Interface;     |

| Clause 8 Interface;  | describes the programming requirements of the AT Attachment |

| Clause 9             | specifies the commands of the AT Attachment Interface;      |

| Clause 10 Interface; | describes an overview of the protocol of the AT Attachment  |

| Clause 11            | specifies the interface timing diagrams;                    |

| Annex A              | describes diagnostic and reset considerations;              |

| Annex B              | describes diagnostic and reset considerations;              |

| Annex C              | describes alternative connectors.                           |

When the first IBM PC (Personal Computer)(tm) was introduced, there was no hard disk capability for storage. Successive generations of product resulted in the inclusion of a hard disk as the primary storage device. When the PC AT (tm) was developed, a hard disk was the key to system performance, and the controller interface became a de facto industry interface for the inclusion of hard disks in PC ATs.

The price of desktop systems has declined rapidly because of the degree of integration to reduce the number of components and interconnects required to build a product. A natural outgrowth of this integration was the inclusion of controller functionality into the hard disk.

In October 1988 a number of peripheral suppliers formed the Common Access Method Committee to encourage an industry-wide effort to adopt a common software interface to dispatch input/output requests to SCSI peripherals. Although this was the primary objective, a secondary goal was to specify what is known as the AT Attachment interface.

American National Standard for Information Technology -

AT Attachment for Disk Drives

#### 1 Scope

This standard defines the AT Attachment Interface. This standard defines an integrated bus interface between disk drives and host processors. It provides a common point of attachment for systems manufacturers, system integrators, and suppliers of intelligent peripherals.

2 Normative references

None.

3 Definitions, symbols, and abbreviations

For the purposes of this standard, the following definitions apply.

- 3.1 Definitions

- $3.1.1\ ATA\ (AT\ attachment).\ ATA\ defines\ a\ compatible\ register\ set\ and\ a\ 40-pin\ connector\ and\ its\ associated\ signals.$

- 3.1.2 CHS (Cylinder-head-sector). This term defines the addressing mode of the drive as being by physical address.

- 3.1.3 data block. This term describes a data transfer, and is typically a single sector, except when declared otherwise by use of the Set Multiple command.

- $3.1.4\ \mathrm{DMA}$  (Direct memory access). A means of data transfer between peripheral and host memory without processor intervention.

- 3.1.5 LBA (Logical block address). This term defines the addressing mode of the drive as being by the linear mapping of sectors from 1 to n.

- 3.1.6 optional. This term describes features which are not required by the standard. However, if any feature defined by the standard is implemented, it shall be done in the same way as defined by the standard. Describing a feature as optional in the text is done to assist the reader. If there is a conflict between text and tables on a feature described as optional, the table shall be accepted as being correct.

- $3.1.7\ \mathrm{PIO}\ (\mathrm{Programmed\ input/output})$ . A means of data transfer that requires the use of the host processor.

- 3.1.8 reserved. Where this term is used for bits, bytes and fields; the bits, bytes and fields are set aside for future standardization, and shall be zero.

- 3.1.9 VU (Vendor unique). This term is used to describe bits, bytes, fields, code values, and features which are not described in this standard, and may be used in a way that varies between vendors.

## 3.2 Symbols and abbreviations

| AWG | American Wire Gauge   |

|-----|-----------------------|

| LSB | Least significant bit |

| LUN | Logical unit number   |

| MSB | Most significant bit  |

#### 4 General

The application environment for the AT Attachment Interface is any computer which uses an AT Bus or 40-pin ATA interface.

The PC AT= Bus is a widely used and implemented interface for which a variety of peripherals have been manufactured. As a means of reducing size and cost, a class of products has emerged which embed the controller functionality in the drive. These new products utilize the AT Bus fixed disk interface protocol, and a subset of the AT bus. Because of their compatibility with existing AT hardware and software this interface quickly became a de facto industry standard.

The purpose of the ATA standard is to define the de facto implementations.

Software in the Operating System dispatches I/O (Input/Output) requests via the AT Bus to peripherals which respond to direct commands.

#### 4.1 Structure

This standard relies upon specifications of the mechanical and electrical characteristics of the AT Bus and a subset of the AT Bus specifically developed for the direct attachment of peripherals.

Also defined are the methods by which commands are directed to peripherals, the contents of registers and the method of data transfers.

#### 4.2 Conventions

Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in clause 3 or in the text where they first appear. Names of signals, phases, messages, commands, statuses, sense keys, additional sense codes, and additional sense code qualifiers are in all uppercase (e.g., REQUEST SENSE). Lower case is used for words having the normal English meaning.

Fields containing only one bit are usually referred to as the "name" bit instead of the "name" field.

Numbers that are not immediately followed by lower-case "b" or "h" are decimal values.

Numbers immediately followed by lower-case "b" (xxb) are binary values.

Numbers immediately followed by lower-case "h" (xxh) are hexadecimal values.

## 5 Interface cabling requirements

### 5.1 Configuration

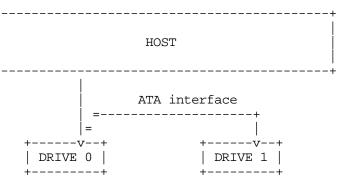

This standard provides the capability of operating on the AT Bus in a daisy chained configuration with a second drive that operates in accordance with these standards. One drive (selected as Drive 0) has been referred to as the master in industry terms and the second (selected as Drive 1) has been referred to as the slave (see figure 3).

The designation as Drive 0 or Drive 1 may be made in a number of ways:

- a switch on the drive;

- a jumper plug on the drive;

- use of the Cable Select (CSEL) pin.

Data is transferred in parallel (8 or 16 bits) either to or from host memory to the drive's buffer under the direction of commands previously transferred from the host. The drive performs all of the operations necessary to properly write data to, or read data from, the disk media. Data read from the media is stored in the drive's buffer pending transfer to the host memory and data is transferred from the host memory to the drive's buffer to be written to the media.

Figure 1 - ATA interface to embedded bus peripherals

Figure 2 - Host bus adapter and peripheral devices

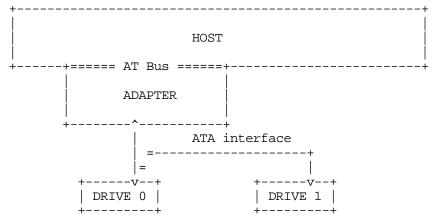

Figure 3 - ATA interface to controller and peripheral devices

### 5.2 Addressing considerations

In traditional controller operation, only the selected controller receives commands from the host following selection. In this standard, the register contents go to both drives (and their embedded controllers). The host discriminates between the two by using the DRV bit in the Drive/Head Register.

## 5.2.1 DC cable and connector

The drive receives DC power through a 4-pin or a low-power application 3-pin connector.

A drive designed for 3,3V applications may be plugged into a receptable designed to accept a drive designed for 5V applications, with 12V lines for additional power. It is not required that the drive operate, but it is recommended that precautions be taken to prevent damage to the drive.

A drive designed for 5V applications may be plugged into a receptacle designed to accept a drive designed for 3,3V applications, with 5V lines for additional power. It is not anticipated that damage could occur to the drive, but it is likely to fail in an undetermined manner.

#### 5.2.2 4-pin power

The pin assignments are shown in table 1. Recommended part numbers for the mating connector to 18 AWG cable are shown below, but equivalent parts may be used.

Connector (4 pin) AMP 1-480424-0 or equivalent.

Contacts (loose piece) AMP 60619-4 or equivalent.

Contacts (strip) AMP 61117-4 or equivalent.

Table 1 - DC interface

| +==============+                        |            |  |  |  |  |  |  |  |

|-----------------------------------------|------------|--|--|--|--|--|--|--|

| Power line designation                  | Pin number |  |  |  |  |  |  |  |

|                                         |            |  |  |  |  |  |  |  |

| +12V                                    | 1-01       |  |  |  |  |  |  |  |

| +12V Return                             | 1-02       |  |  |  |  |  |  |  |

| +5V Return                              | 1-03       |  |  |  |  |  |  |  |

| +5V                                     | 1-04       |  |  |  |  |  |  |  |

| +====================================== | =======+   |  |  |  |  |  |  |  |

## 5.2.3 3-pin power

The pin assignments are shown in table 2. Recommended part numbers for the mating connector to 18 AWG cable are shown below, but equivalent parts may be used.

Connector (3 pin)

Molex 5484 39-27-0032 or equivalent.

Table 2 - DC interface

| + | -========             | -======                | -======+             | - |

|---|-----------------------|------------------------|----------------------|---|

|   | Power line o          | designation            | Pin number           |   |

|   | +5V<br>+12V<br>Ground | +3,3V<br>+5V<br>Ground | 1-01<br>1-02<br>1-03 |   |

| + | -========             |                        | ======+              | - |

#### 5.2.4 Device grounding

System ground may be connected to a "quick-connect" terminal equivalent to:

Drive connector terminal

Cable connector terminal

AMP 61664-1 or equivalent. AMP 62137-2 or equivalent.

Provision for tying the DC logic ground and the chassis ground together or for separating these two ground planes is vendor specific.

#### 5.3 I/O connector

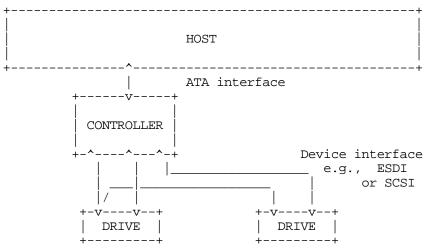

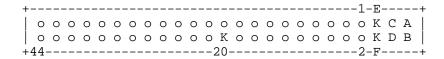

The I/O connector is a 40-pin connector as shown in figure 4, with pin assignments as shown in table 4. The connector should be keyed to prevent the possibility of installing it upside down. A key is provided by the removal of pin 20. The corresponding pin on the cable connector should be plugged.

The pin locations are governed by the cable plug, not the receptacle. The way in which the receptacle is mounted on the printed circuit board affects the pin positions, and pin 1 should remain in the same relative position. This means the pin numbers of the receptacle may not reflect the conductor number of the plug. The header receptacle is not polarized, and all the signals are relative to pin 20, which is keyed.

By using the plug positions as primary, a straight cable can connect drives.

As shown in figure 4, conductor 1 on pin 1 of the plug has to be in the same relative position no matter what the receptacle numbering looks like. If receptacle numbering was followed, the cable would have to twist 180 degrees between a drive with top-mounted receptacles, and a drive with bottom-mounted receptacles.

Figure 4 - 40-pin connector mounting

Recommended part numbers for the mating connector are shown below, but equivalent parts may be used.

```

Connector (40 pin)

Strain relief

Strain cable (stranded 28 AWG)

Flat cable (stranded 28 AWG)

Flat cable (stranded 28 AWG)

Flat cable (stranded 28 AWG)

Grequivalent.

3M 3417-7000 or equivalent.

3M 3448-2040 or equivalent.

3M 3517-40 (shielded) or equivalent.

```

## 5.4 I/O cable

The cable specifications affect system integrity and the maximum length that can be supported in any application as shown in table 3.

Table 3 - Cable parameters

| Cable length of 0,46m (18 inches) *                                                                                                    | -=====<br>  Min | -=====+<br>  Max |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|

| Driver IoL sink current for 5V operation Driver IoL sink current for 3,3V operation Driver IoH source current Cable capacitive loading | 12mA<br>8mA     | -400uA<br>200pF  |

| * This distance may be exceeded in circumstar   characteristics of both ends of the cable car                                          |                 |                  |

### 6 Physical interface

#### 6.1 Signal conventions

Signal names are shown in all upper case letters. Signals can be asserted (active, true) in either a high (more positive voltage) or low (less positive voltage) state. A dash character (-) at the beginning or end of a signal name indicates it is asserted at the low level (active low). No dash or a plus character (+) at the beginning or end of a signal name indicates it is asserted high (active high). An asserted signal may be driven high or low by an active circuit, or it may be allowed to be pulled to the correct state by the bias circuitry.

Control signals that are asserted for one function when high and asserted for another function when low are named with the asserted high function name followed by a slash character (/), and the asserted low function name followed with a dash (-) e.g., BITENA/BITCLR- enables a bit when high and clears a bit when low. All signals are TTL compatible unless otherwise noted. Negated means that the signal is driven by an active circuit to the state opposite to the asserted state (inactive, or false) or may be simply released (in which case the bias circuitry pulls it inactive, or false), at the option of the implementor.

Control signals that may be used for two mutually exclusive functions are identified with their two names separated by a colon e.g., SPSYNC:CSEL can be used for either the Spindle Sync or the Cable Select functions.

#### 6.2 Signal summary

The physical interface consists of single ended TTL compatible receivers and drivers communicating through a 40-conductor flat ribbon non-shielded cable using an asynchronous interface protocol. The pin numbers and signal names are shown in table 4. Reserved signals shall be left unconnected.

Table 4 - Interface signals

| +======================================                                          |          |        |                           | _         |

|----------------------------------------------------------------------------------|----------|--------|---------------------------|-----------|

| Host I/O                                                                         |          | <br>   | <br>                      | Drive I/O |

| connector                                                                        |          | İ      | İ                         | connector |

|                                                                                  |          | ,<br>+ | י<br>++                   |           |

| HOST RESET                                                                       | 1        |        | RESET>                    | 1         |

|                                                                                  | 2        |        | Ground                    | 2         |

| HOST DATA BUS BIT 7                                                              | 3        | <      | DD7>                      | 3         |

| HOST DATA BUS BIT 8                                                              |          | <      | DD8>                      | 4         |

| HOST DATA BUS BIT 6<br>HOST DATA BUS BIT 9                                       | 5        | <      | DD6>                      | 5         |

| HOST DATA BUS BIT 9                                                              | 6        | <      | DD9>                      | 6         |

| HOST DATA BUS BIT 9 HOST DATA BUS BIT 5 HOST DATA BUS BIT 10 HOST DATA BUS BIT 4 | 7        |        | DD5>                      | 7         |

| HOST DATA BUS BIT 10                                                             | 8        |        | DD10>                     |           |

| HOST DATA BUS BIT 4                                                              | 9        |        | DD4>                      |           |

| HOST DATA BUS BIT 11                                                             | 10       | <      | DD11>                     | 10        |

| HOST DATA BUS BIT 3                                                              | 11       | <      | DD3>                      | 11        |

| HOST DATA BUS BIT 11 HOST DATA BUS BIT 3 HOST DATA BUS BIT 12                    | 12       | !      | DD12>                     |           |

|                                                                                  |          | <      | DD2>                      | 13        |

| HOST DATA BUS BIT 2 HOST DATA BUS BIT 13                                         |          | 1      | DD13>                     |           |

| HOST DATA BUS BIT 1<br>HOST DATA BUS BIT 14                                      | 15       |        | DD1>                      |           |

| HOST DATA BUS BIT 14                                                             | 16       |        | DD14>                     |           |

| HOST DATA BUS BIT 0                                                              | 17       |        | DD0>                      |           |

| HOST DATA BUS BIT 15                                                             | 17<br>18 | !      | DD15>                     |           |

|                                                                                  | 19       | 1      | Ground                    |           |

|                                                                                  | 20       |        | (keypin)                  |           |

| DMA REQUEST                                                                      |          | !      | DMARQ                     |           |

|                                                                                  | 22       | !      | Ground                    |           |

| HOST I/O WRITE                                                                   |          |        | DIOW>                     |           |

|                                                                                  |          |        | Ground                    |           |

| HOST I/O READ                                                                    | 25       | !      | DIOR>                     |           |

|                                                                                  | 26       | 1      | Ground                    |           |

| I/O CHANNEL READY                                                                | 27       | !      | IORDY                     |           |

| SPINDLE SYNC or CABLE SELECT                                                     |          | !      | PSYNC:CSEL*               |           |

| DMA ACKNOWLEDGE                                                                  |          | 1      | DMACK>                    |           |

|                                                                                  | 30       | :      | Ground                    |           |

| HOST INTERRUPT REQUEST                                                           | 31       | <      | INTRQ                     | 31        |

| HOST 16 BIT I/O                                                                  | 32       | <      | IOCS16 <br>DA1 <br>PDIAG* | 32        |

| HOST ADDRESS BUS BIT 1                                                           | 33       |        | DA1>                      | 33        |

| PASSED DIAGNOSTICS                                                               | 34       | *      | PDIAG*                    | 34        |

| HOST ADDRESS BUS BIT 0                                                           | 35       |        | DAO> DA2>                 | 35        |

| HOST ADDRESS BUS BIT 2                                                           | 36       |        | DAZ>                      | 36        |

| HOST CHIP SELECT 0                                                               | 37       |        | CS1FX>   CS3FX>           | 37        |

| HOST CHIP SELECT 1                                                               | 38       |        | CS3FX>                    | 38        |

| DRIVE ACTIVE/DRIVE 1 PRESENT                                                     |          |        |                           |           |

|                                                                                  | 40       | •      | Ground                    |           |

|                                                                                  |          |        |                           |           |

| *Drive intercommunication s                                                      |          |        |                           |           |

+=============++

| +HOST+ |   | Dri | ve 0 | + -            | Drive 1-+ |

|--------|---|-----|------|----------------|-----------|

| 28     | > | 28  | 28   | < SPSYNC:CSEL> | 28        |

| 34     |   | 34  | 34   | < PDIAG        | 34        |

| 39     | < | 39  | 39   | < DASP         | 39        |

| ++     |   |     |      | +              | +         |

## 6.3 Signal descriptions

The interface signals and pins are described in more detail than shown in table 4. The signals are listed according to function, rather than in numerical connector pin order. Table 5 lists signal name mnemonic, connector pin number, whether input to (I) or output from (O) the drive, and full signal name.

Table 5 - Interface signals description

| Signal  | Pin |     | -=====================================      |

|---------|-----|-----|---------------------------------------------|

| CS1FX-  | 37  | I   | Drive chip select 0                         |

| CS3FX-  | 38  | I   | Drive chip select 1                         |

| DA0     | 35  | I   | Drive address bus - bit 0                   |

| DA1     | 33  | I   | - bit 1                                     |

| DA2     | 36  | I   | - bit 2                                     |

| DASP-   | 39  | I/O | Drive active/drive 1 present                |

| DD0     | 17  | I/O | Drive data bus - bit 0                      |

| DD1     | 15  | I/O | - bit 1                                     |

| DD2     | 13  | I/O | - bit 2                                     |

| DD3     | 11  | I/O | - bit 3                                     |

| DD4     | 9   | I/O | - bit 4                                     |

| DD5     | 7   | I/O | - bit 5                                     |

| DD6     | 5   | I/O | - bit 6                                     |

| DD7     | 3   | I/O | - bit 7                                     |

| DD8     | 4   | I/O | - bit 8                                     |

| DD9     | 6   | I/O | - bit 9                                     |

| DD10    | 8   | I/O | - bit 10                                    |

| DD11    | 10  | I/O | - bit 11                                    |

| DD12    | 12  | I/O | - bit 12                                    |

| DD13    | 14  | I/O | - bit 13                                    |

| DD14    | 16  | I/O | - bit 14                                    |

| DD15    | 18  | I/O | - bit 15                                    |

| DIOR-   | 25  | I   | Drive I/O read                              |

| DIOW-   | 23  | I   | Drive I/O write                             |

| DMACK-  | 29  | I   | DMA acknowledge                             |

| DMARQ   | 21  | 0   | DMA request                                 |

| INTRO   | 31  | 0   | Drive interrupt                             |

| IOCS16- | 32  | 0   | Drive 16-bit I/O                            |

| IORDY   | 27  | 0   | I/O channel ready                           |

| PDIAG-  | 34  | I/O | Passed diagnostics                          |

| RESET-  | 1   | I   | Drive reset                                 |

| SPSYNC: | 28  | _   | Spindle sync                                |

| CSEL    | 28  | _   | Cable select                                |

| keypin  | 20  | _   | Pin used for keying the interface connector |

### 6.3.1 CS1FX- (drive chip select 0)

This is the chip select signal decoded from the host address bus used to select the Command Block Registers.

#### 6.3.2 CS3FX- (drive chip select 1)

This is the chip select signal decoded from the host address bus used to select the Control Block Registers.

#### 6.3.3 DA0-2 (Drive address bus)

This is the 3-bit binary coded address asserted by the host to access a register or data port in the drive.

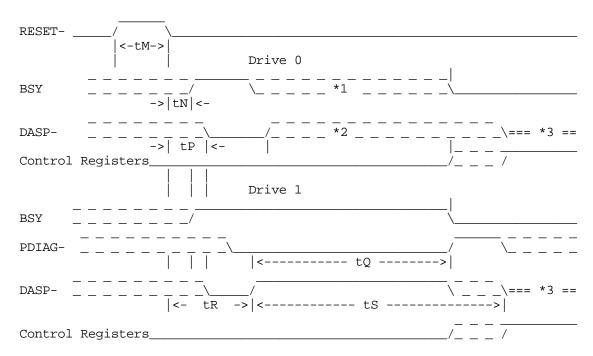

#### 6.3.4 DASP- (Drive active/drive 1 present)

This is a time-multiplexed signal which indicates that a drive is active, or that Drive 1 is present. This signal shall be an open collector output and each drive shall have a 10K ohm pull-up resistor.

During power on initialization or after RESET- is negated, DASP- shall be asserted by Drive 1 within 400 msec to indicate that Drive 1 is present.

Drive 0 shall allow up to 450 msec for Drive 1 to assert DASP-. If Drive 1 is not present, Drive 0 may assert DASP- to drive an activity LED.

DASP- shall be negated following acceptance of the first valid command by Drive 1 or after 31 seconds, whichever comes first.

Any time after negation of DASP-, either drive may assert DASP- to indicate that a drive is active.

NOTE 1 - Prior to the development of this standard, products were introduced which did not time multiplex DASP-. Some used two jumpers to indicate to Drive 0 whether Drive 1 was present. If such a drive is jumpered to indicate Drive 1 is present it should work successfully with a Drive 1 which complies with this standard. If installed as Drive 1, such a drive may not work successfully because it may not assert DASP- for a long enough period to be recognized. However, it would assert DASP-to indicate that the drive is active.

#### 6.3.5 DD0-DD15 (Drive data bus)

This is an 8- or 16-bit bidirectional data bus between the host and the drive. The lower 8 bits are used for 8-bit transfers e.g., registers, ECC bytes and, if the drive supports the Features Register capability to enable 8-bit-only data transfers (see 9.22).

#### 6.3.6 DIOR- (Drive I/O read)

This is the Read strobe signal. The falling edge of DIOR- enables data from a register or the data port of the drive onto the host data bus, DDO-DD7 or DDO-DD15. The rising edge of DIOR- latches data at the host.

### 6.3.7 DIOW- (Drive I/O write)

This is the Write strobe signal. The rising edge of DIOW- clocks data from the host data bus, DDO-DD7 or DDO-DD15, into a register or the data port of the drive.

#### 6.3.8 DMACK- (DMA acknowledge) (Optional)

This signal shall be used by the host in response to DMARQ to either acknowledge that data has been accepted, or that data is available.

### 6.3.9 DMARQ (DMA request) (Optional)

This signal, used for DMA data transfers between host and drive, shall be asserted by the drive when it is ready to transfer data to or from the host. The direction of data transfer is controlled by DIOR- and DIOW-. This signal is used in a handshake manner with DMACK- i.e., the drive shall wait until the host asserts DMACK- before negating DMARQ, and re-asserting DMARQ if there is more data to transfer.

When a DMA operation is enabled, IOCS16-, CS1FX-, and CS3FX- shall not be asserted and transfers shall be 16-bits wide.

NOTE 2 - ATA products with DMA capability require a pull-down resistor on this signal to prevent spurious data transfers. This resistor may affect driver requirements for drives sharing this signal in systems with unbuffered ATA signals.

### 6.3.10 INTRQ (Drive interrupt)

This signal is used to interrupt the host system. INTRQ is asserted only when the drive has a pending interrupt, the drive is selected, and the host has cleared nIEN in the Device Control Register. If nIEN=1, or the drive is not selected, this output is in a high impedance state, regardless of the presence or absence of a pending interrupt.

INTRQ shall be negated by:

- assertion of RESET- or;

- the setting of SRST of the Device Control Register, or;

- the host writing the Command Register or;

- the host reading the Status Register.

NOTE 3 - Some drives may negate INTRQ on a PIO data transfer completion, except on a single sector read or on the last sector of a multi-sector read.

On PIO transfers, INTRQ is asserted at the beginning of each data block to be transferred. A data block is typically a single sector, except when declared otherwise by use of the Set Multiple command. An exception occurs on Format Track, Write Sector(s), Write Buffer and Write Long commands - INTRQ shall not be asserted at the beginning of the first data block to be transferred.

On DMA transfers, INTRQ is asserted only once, after the command has completed.

### 6.3.11 IOCS16- (Drive 16-bit I/O)

Except for DMA transfers, IOCS16- indicates to the host system that the 16-bit data port has been addressed and that the drive is prepared to send or receive a 16-bit data word. This shall be an open collector output.

- When transferring in PIO mode, if IOCS16- is not asserted, transfers shall be 8-bit using DD0-7.

- When transferring in PIO mode, if IOCS16- is asserted, transfers shall be 16-bit using DD0-15.

- When transferring in DMA mode, the host shall use a 16-bit DMA channel and IOCS16- shall not be asserted.

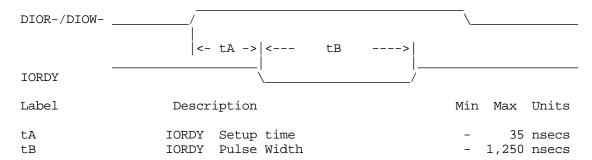

#### 6.3.12 IORDY (I/O channel ready) (Optional)

This signal is negated to extend the host transfer cycle of any host register access (Read or Write) when the drive is not ready to respond to a data transfer request. When IORDY is not negated, IORDY shall be in a high impedance state.

### 6.3.13 PDIAG- (Passed diagnostics)

This signal shall be asserted by Drive 1 to indicate to Drive 0 that it has completed diagnostics. A 10K ohm pull-up resistor shall be used on this signal by each drive.

Following a power on reset, software reset or RESET-, Drive 1 shall negate PDIAG- within 1 msec (to indicate to Drive 0 that it is busy). Drive 1 shall then assert PDIAG- within 30 seconds to indicate that it is no longer busy, and is able to provide status. If Drive 1 is present, then Drive 0 shall wait for up to 31 seconds from power-on reset, software reset or RESET- for Drive 1 to assert PDIAG-. If Drive 1 fails to assert PDIAG-, Drive 0 shall set bit 7 to 1 in the Error Register to indicate that Drive 1 failed. After the assertion of PDIAG-, Drive 1 may be unable to accept commands until it has finished its reset procedure and is Ready (DRDY=1).

Following the receipt of a valid Execute Drive Diagnostics command, Drive 1 shall negate PDIAG- within 1 msec to indicate to Drive 0 that it is busy and has not yet passed its drive diagnostics. Drive 1 shall then assert PDIAG-within 5 seconds to indicate that it is no longer busy, and is able to provide status. Drive 1 should clear BSY before asserting PDIAG-. If Drive 1 is present then Drive 0 shall wait for up to 6 seconds from the receipt of a valid Execute Drive Diagnostics command for Drive 1 to assert PDIAG-. If Drive 1 fails to assert PDIAG-, Drive 0 shall set bit 7 to 1 in the Error Register to indicate that Drive 1 failed.

If DASP- was not asserted by Drive 1 during reset initialization, Drive 0 shall post its own status immediately after it completes diagnostics, and clear the Drive 1 Status Register to 00h. Drive 0 may be unable to accept commands until it has finished its reset procedure and is Ready (DRDY=1).

### 6.3.14 RESET- (Drive reset)

This signal from the host system shall be asserted for at least 25 usec after voltage levels have stabilized during power on and negated thereafter unless some event requires that the drive(s) be reset following power on.

#### 6.3.15 SPSYNC:CSEL (Spindle synchronization/cable select) (Optional)

This signal shall have a 10K ohm pull-up resistor.

This is a dual purpose signal and either or both functions may be implemented. If both functions are implemented then they cannot be active concurrently: the choice as to which is active is made by a vendor-defined switch.

All drives connected to the same cable should have the same function active at the same time. If SPSYNC and CSEL are mixed on the same cable, then drive behavior is undefined.

Prior to the introduction of this standard, this signal was defined as DALE (Drive Address Latch Enable), and used for an address valid indication from the host system. If used, the host address and chip selects, DAO through DA2, CS1FX-, and CS3FX- were valid at the negation of this signal and remained valid while DALE was negated, therefore, the drive did not need to latch these signals with DALE.

### 6.3.16 SPSYNC (Spindle synchronization) (Optional)

This signal may be either input or output to the drive depending on a vendor-defined switch. If a drive is set to Master the signal is output, and if a drive is set to slave the signal is input.

There is no requirement that each drive implementation be plug-compatible to the extent that a multiple vendor drive subsystem be operable. Mix and match of different manufacturers drives is unlikely because rpm, sync fields, sync bytes, etc., need to be virtually identical. However, if drives are designed to match the following recommendation, controllers can operate drives with a single implementation.

There can only be one master drive at a time in a configuration. The host or the drive designated as master can generate SPSYNC at least once per rotation, but may be at a higher frequency.

SPSYNC received by a drive is used as the synchronization signal to lock the spindles in step. The time to achieve synchronization varies, and is indicated by the drive setting DRDY i.e., if the drive does not achieve synchronization following power on or a reset, it shall not set DRDY.

A master drive or the host generates SPSYNC and transmits it.

A slave drive does not generate SPSYNC and is responsible to synchronize its index to SPSYNC.

If a drive does not support synchronization, it shall ignore SPSYNC.

In the event that a drive previously synchronized loses synchronization, but is otherwise operational, it does not clear DRDY.

## 6.3.17 CSEL (Cable select) (Optional)

The drive is configured as either Drive 0 or Drive 1 depending upon the value of CSEL:

- If CSEL is grounded then the drive address is 0;

- If CSEL is open then the drive address is 1.

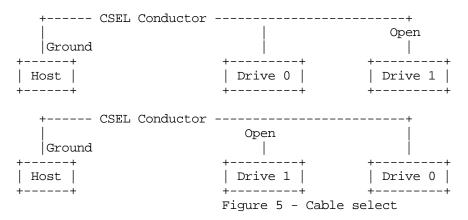

Special cabling can be used by the system manufacturer to selectively ground CSEL e.g., CSEL of Drive 0 is connected to the CSEL conductor in the cable, and is grounded, thus allowing the drive to recognize itself as Drive 0. CSEL of Drive 1 is not connected to CSEL because the conductor is removed, thus the drive can recognize itself as Drive 1. See figure 5.

7 Logical interface

#### 7.1 General

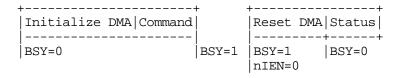

### 7.1.1 Bit conventions

Bit names are shown in all upper case letters except where a lower case n precedes a bit name. This indicates that when nBIT=0 (bit is zero) the action is true and when nBIT=1 (bit is one) the action is false. If there is no preceding n, then when BIT=1 it is true, and when BIT=0 it is false.

A bit can be set to one or cleared to zero and polarity influences whether it is to be interpreted as true or false:

| True  | BIT=1 | nBIT=0 |

|-------|-------|--------|

| False | BIT=0 | nBIT=1 |

### 7.1.2 Environment

The drives using this interface shall be programmed by the host computer to perform commands and return status to the host at command completion. When two drives are daisy chained on the interface, commands are written in parallel to both drives, and for all except the Execute Diagnostics command, only the selected drive executes the command. On an Execute Diagnostics command addressed to Drive 0, both drives shall execute the command, and Drive 1 shall post its status to Drive 0 via PDIAG-.

Drives are selected by the DRV bit in the Drive/Head Register (see 7.2.8), and by a jumper or switch on the drive designating it as either a Drive 0 or as Drive 1. When DRV=0, Drive 0 is selected. When DRV=1, Drive 1 is selected. When drives are daisy chained, one shall be set as Drive 0 and the other as Drive 1. When a single drive is attached to the interface it shall be set as Drive 0.

Prior to the adoption of this standard, some drives may have provided jumpers to indicate Drive 0 with no Drive 1 present, or Drive 0 with Drive 1 present. Throughout this document, drive selection always refers to the state of the DRV bit, the position of the Drive 0/Drive 1 jumper or switch, or use of the CSEL pin.

A drive can operate in either of two addressing modes, CHS or LBA, on a command by command basis. A drive which can support LBA mode indicates this in the Identify Drive Information. If the host selects LBA mode in the Drive/Head register, Sector Number, Cylinder Low, Cylinder High and HS3-HS0 of the Drive/Head Register contains the zero based-LBA.

In LBA mode, the sectors on the drive are assumed to be linearly mapped with an Initial definition of:

LBA 0 = Cylinder 0/head 0/sector 1.

Irrespective of translate mode geometry set by the host, the LBA address of a given sector does not change:

LBA = [ (Cylinder \* no of heads + heads) \* sectors/track ] + (Sector-1)

## 7.2 I/O register descriptions

Communication to or from the drive is through an I/O Register that routes the input or output data to or from registers (selected) by a code on signals from the host (CS1FX-, CS3FX-, DA2, DA1, DA0, DIOR-, and DIOW-).

The Command Block Registers are used for sending commands to the drive or posting status from the drive.

The Control Block Registers are used for drive control and to post alternate status.

Table 6 lists these registers and the addresses that select them.

Logic conventions are:

A = signal asserted;

N = signal negated;

x = does not matter which it is.

Table 6 - I/O port functions/selection addresses

|                                           | Addre                                 | esses                                               |                                                          |                         | Functions                                                                                                                                                                     |                                                                                                                                                                          |  |  |

|-------------------------------------------|---------------------------------------|-----------------------------------------------------|----------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                           |                                       |                                                     |                                                          |                         | READ (DIOR-)                                                                                                                                                                  | WRITE (DIOW-)                                                                                                                                                            |  |  |

| CS1FX-                                    | CS3FX- <br>                           | DA2                                                 | DA1                                                      | DA0                     | Control block                                                                                                                                                                 | registers                                                                                                                                                                |  |  |

| N<br>N                                    | N  <br>  A                            | x<br>0                                              | x<br>  x                                                 | x<br>  X                | Data bus high imped<br>Data bus high imped                                                                                                                                    | 1                                                                                                                                                                        |  |  |

| N<br>N<br>N                               | A<br>  A  <br>  A                     | 1 1                                                 | 0<br>  1<br>  1                                          | x<br>  0<br>  1         | Data bus high imped<br>Alternate status<br>Drive address                                                                                                                      | Not used<br>Device control<br>Not used                                                                                                                                   |  |  |

|                                           |                                       | Command block registers                             |                                                          |                         |                                                                                                                                                                               |                                                                                                                                                                          |  |  |

| A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A | N N N N N N N N N N N N N N N N N N N | 0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0 1 1 0 0 1 1 0 0 0 1 x | Data Error register Sector count Sector number * LBA bits 0- 7 Cylinder low * LBA bits 8-15 Cylinder high * LBA bits 16-23 Drive/head * LBA bits 24-27 Status Invalid address | Data Features Sector count Sector number * LBA bits 0- 7 Cylinder low * LBA bits 8-15 Cylinder high * LBA bits 16-23 Drive/head * LBA bits 24-27 Command Invalid address |  |  |

+------

## 7.2.1 Alternate status register

This register contains the same information as the Status Register in the command block. The only difference being that reading this register does not imply interrupt acknowledge or clear a pending interrupt.

| 4 | -====== | -====== | -====== | -====== | -====== | -====== | -====== | -=====+ |

|---|---------|---------|---------|---------|---------|---------|---------|---------|

|   | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| j |         | +       | +       | +       |         | +       | +       | +       |

| į | BSY     | DRDY    | DWF     | DSC     | DRQ     | CORR    | IDX     | ERR     |

See 7.2.13 for definitions of the bits in this register.

#### 7.2.2 Command register

This register contains the command code being sent to the drive. Command execution begins immediately after this register is written. The executable commands, the command codes, and the necessary parameters for each command are listed in table 9.

### 7.2.3 Cylinder high register

This register contains the high order bits of the starting cylinder address for any disk access. At the end of the command, this register is updated to reflect the current cylinder number. The most significant bits of the cylinder address shall be loaded into the cylinder high Register.